패키징의 정의

외부환경으로부터 보호하고 단자간 연결을 위한 전기적인 포장. 반도체 칩을 탑재될 기기에 적합한 형태로 포장한다

PCB - Printed Circuit Board (인쇄 회로 기판)

- 컴퓨터를 열어보았을 때 mother board의 초록 색상이다

- 전자부품을 PCB에 고정하고 부품사이를 구리 배선으로 연결해 전자회로를 구성한다

- 전선의 배선이 인쇄되기에 인쇄회로로 불린다

- 목적에 맞게 설계와 두께가 정해진다

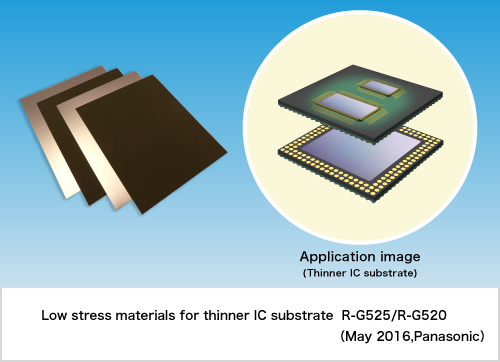

패키징용 PCB - SUBSTRATE PCB / IC Substrate

- 전자회로 구성용 PCB보다 얇으며 DIE의 전기적 인출을 담당한다

- PCB가 전자부품을 실장하는 기판이라면 IC Substrate는 Chip을 실장하는 기판이다

- 칩을 패키지 기판(IC Substrate)에 실장한 뒤 칩을 몰딩한 후에 메인기판(PCB)에 실장한다

IC Substrate (반도체 기판) vs PCB의 차이

패키징쪽을 보면서 가장 오랫동안 헷갈렸던 부분이다. IC 기판과 PCB가 어떤 식으로 다른지.... 막상 제대로 이해하고 나니 정말 별것 없지만 처음에는 굉장히 헷갈린다. 위 사진은 컴퓨터 메인보

hunter-trader.tistory.com

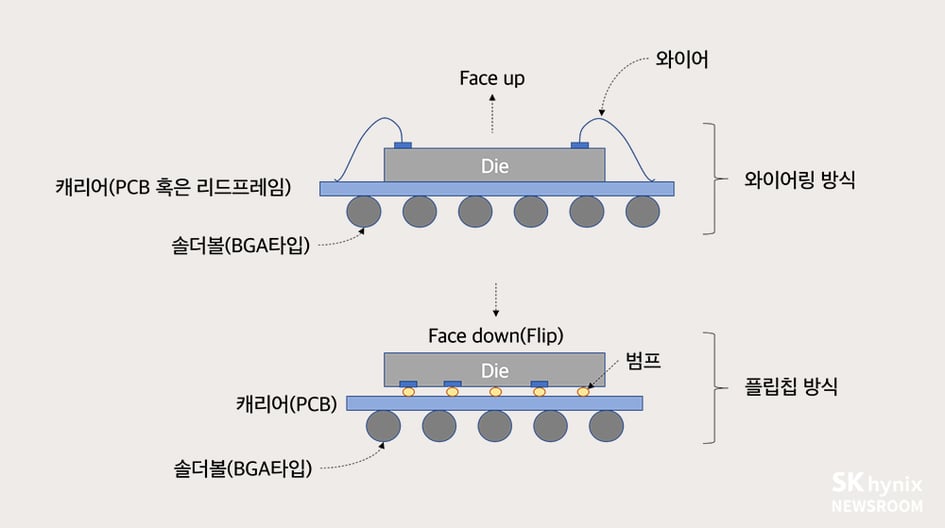

CONVENTIONAL PACKAGE의 두가지 방법

- 전통적 방식인 WIRE BONDING (WB공정) 을 통한 DIE와 PCB 배선

- DIE와 PCB를 납땜 방식으로 붙이는 FLIP CHIP 공정

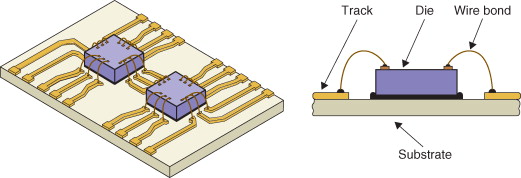

와이어본딩 Wire Bonding

- 와이어 본딩(Wirebonding)은 실리콘 칩과 반도체 디바이스의 외부 선을 매우 미세한 배선으로 전기적 연결을 하는 공정

- Wirebonding에 사용되는 배선은 대게 Au나 Al 계열이 많이 쓰이며 Cu 도 반도체 제조 산업에서 쓰이기 시작

- Au는 산화작용이 적어 bonding 시 크게 문제가 되지 않으나 Cu의 경우 산화되는 것을 방지하기 위해 wirebonding 공정 중에 질소 가스를 사용해야 한다

- Cu는 Au 보다 강하기 때문에 칩의 표면에 쉽게 대미지를 줄 수 있다

- 어쨋거나 Cu는 Au보다 값이 싸고 전기적으로 우수한 성질을 가지고 있으므로 상황에 맞게 선택

- 일반적인 패키지에서 다이와 캐리어의 접합은 와이어(wire)를 이용한다

- 다이는 캐리어의 표면에 접착되고, 와이어로 다이와 캐리어를 연결함

반도체 패키징 공정 와이어 본딩

Wire bonding 이란? 반도체 패키징 공정 중의 와이어 본딩(Wirebonding)은 실리콘 칩과 반도체 디바이스의 외부 선을 매우 미세한 배선으로 전기적 연결을 하는 공정이다. Wirebonding에 사용되는 배선은

mecaji.tistory.com

[반도체 특강] 와이어본딩(Wire Bonding), 칩을 바느질해 PCB에 연결하다

반도체 전(前)공정을 마친 웨이퍼에는 장당 500~1,200개의 칩(다이, Die)이 달라붙어 있습니다

news.skhynix.co.kr

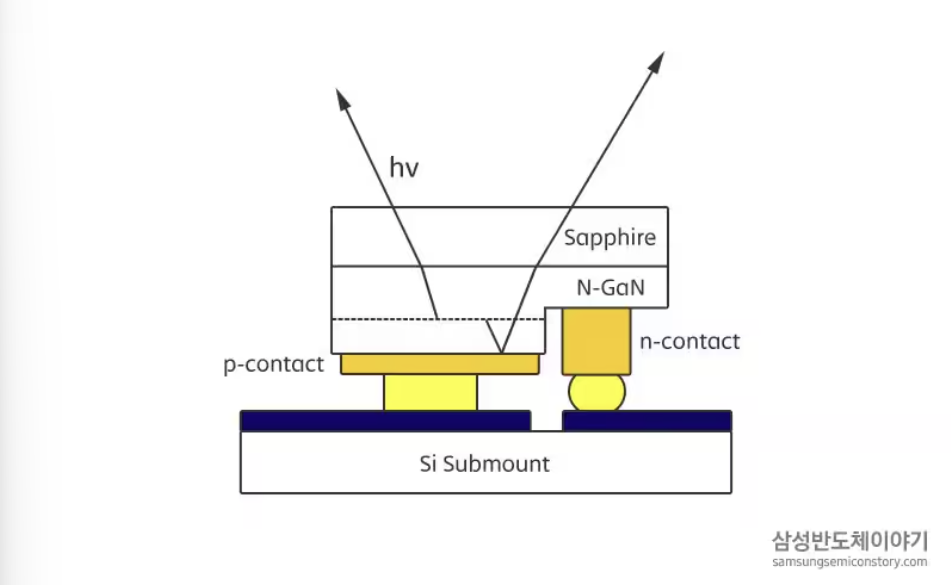

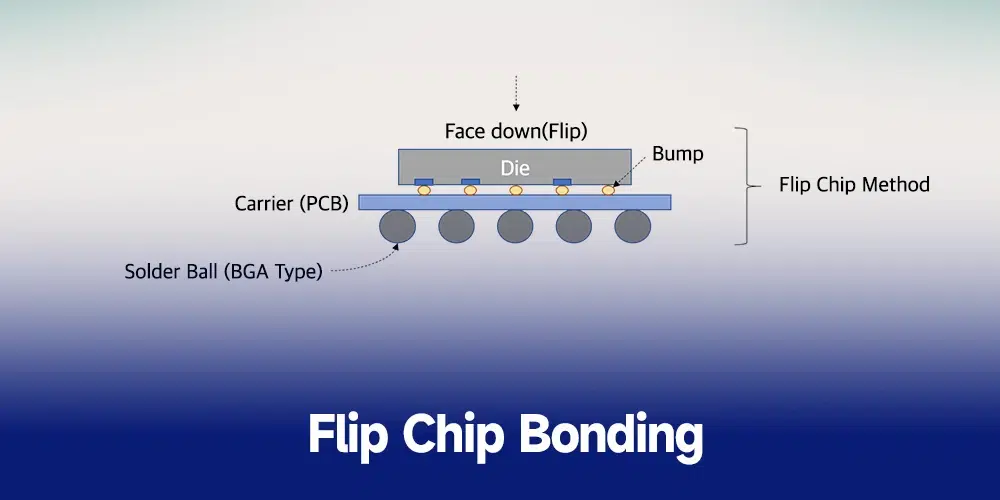

Flip Chip

- 반도체 칩을 회로 기판에 부착시킬 때 금속 리드(와이어)와 같은 추가적인 연결구조나 볼그리드어레이(BGA)와 같은 중간 매체를 사용하지 않고 칩 아랫면의 전극 패턴을 이용해 그대로 융착시키는 방식

- 선이 없는(Leadless) 반도체라고도 한다

- 패키지가 칩 크기와 같아 소형, 경량화에 유리하고 전극 간 거리를 훨씬 미세하게 만들 수 있는 것이 특징

플립칩 | Samsung Semiconductor KR

삼성반도체 공식 웹사이트 기술 블로그에서 플립칩 [Flip Chip]에 대해 알아보세요.

semiconductor.samsung.com

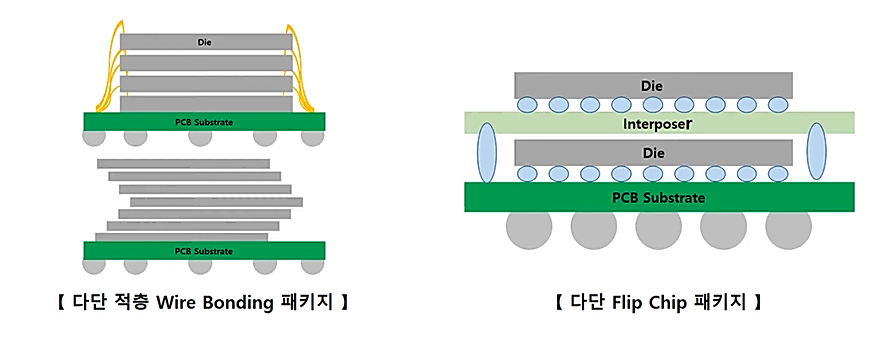

CONVENTIONAL PACKAGE의 발전

- WIRE BONDING: 주로 메모리 제품에 활용, 다단 적층에 유리, 가격, 전기적 성능 DOWN

- 메모리 제품의 예 - NAND, DRAM, FLASH

- FLIP-CHIP: 주로 비메모리 제품에 활용, WB 대비 빠른 전기 인출, 가격, 전기적 성능 UP

- 비메모리 제품의 예 - AP, CPU

플립칩의 장점

- 신호(signal) 저항 계수 감소 - 다이와 캐리어의 거리가 짧아짐에 따라, 신호 저항 계수가크게 감소 - 이것이 바로 초고속의 통신과 스위칭 장치(switching device)의 핵심 적인 요소

- 전기(power/ground) 저항 계수의 감소 - 플립칩 접합 기술을 사용함에 따라, 종전의 다이 끝 부분을 통해 우회하던 전기신호가 다이의 핵심부분으로 바로 이동하게 됨. 이를 통해 핵심전력의 노이즈(noise)를 줄이게 되고 칩의 성능을 개선

- 높은 신호(signal) 집적- 종전의 다이의 측면만을 이용한 방식에서 벗어나 다이의 전면을 접점으로 이용함에따라 집적도를 높일 수 있게 됨. 이것은 QFP와 BGA 패키지를 비교하는 것과 비슷함. 플립칩은 다이의 전면을 접점으로 사용함에 따라 작은 다이에서도 상당한 량의 접점을 만들어 낼 수 있다

- 다이 사이즈 감소 - 필요한 본드 패드(bond pads)의 수량(면적)에 의해 다이의 사이즈가 결정되던 종래의 방식을벗어남으로 그 만큼의 다이 사이즈를 줄일 수 있게 되고 실리콘 비용을 줄일 수 있게 된다

- 패키지 풋프린트(footprint) 감소 - 어떤 경우에는 플립칩 기술을 사용함에 따라 전체적인 패키지 사이즈가 줄게 됨. 패키지 사이즈 감소는 와이본딩을 위한 공간을 없애고, 집적도 높은 기판을 사용함으로써 가능하게 된다

- 플립칩의 장점 출처: https://toparadic.tistory.com/278

플립 칩(Flip Chip)

반도체 칩을 회로 기판에 부착시킬 때 금속 리드(와이어)와 같은 추가적인 연결구조나 볼그리드어레이(BGA)와 같은 중간 매체를 사용하지 않고 칩 아랫면의 전극 패턴을 이용해 그대로 융착시키

toparadic.tistory.com

CONVENTIONAL PACKAGE의 변화, 진화

- WIRE BONDING: 다단 적층에 유리 (경박단소 - 가볍고 얇고 작다)

- FLIP-CHIP : 다단이 가능하지만 WB만큼 높게 쌓을 수 없다

- V-NAND: 위로만 쌓아 올릴 수 없기 떄문에 DIE를 V자로 쌓아 올리는 형태

V 낸드 독창성의 다음 단계 | 삼성반도체

삼성전자는 V낸드 기술을 도입하여 기존 2차원 낸드 플래시 스토리지 메모리를 벗어나 차세대 스토리지 솔루션을 제공했습니다.

semiconductor.samsung.com

PCB동도금기술

인쇄회로기판(PCB)의 여러공정중에 중요하지 않은 공정은 하나도 없다. 사소한 부주의가 어이없는 불량...

blog.naver.com

그림으로 보는 PCB공정

PCB공정을 이해하는데 도움이 될것 같아 PCB의 주요공정을 그림으로 나타냈다. PCB는 장치산업이...

blog.naver.com

[반도체산업]PCB(인쇄회로기판)이란? - 2편

PCB(인쇄회로기판) 시리즈 링크 PCB(인쇄회로기판)이란? - 1편 (메인기판의 종류와 용어정리) IC ...

blog.naver.com

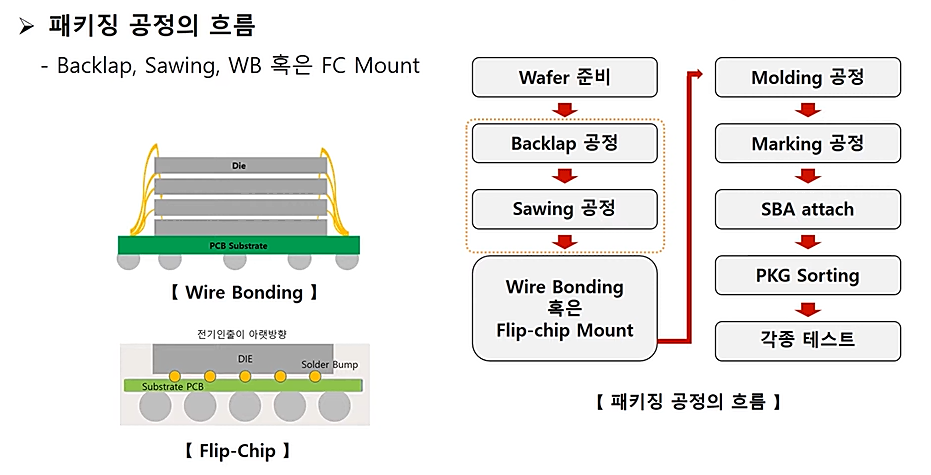

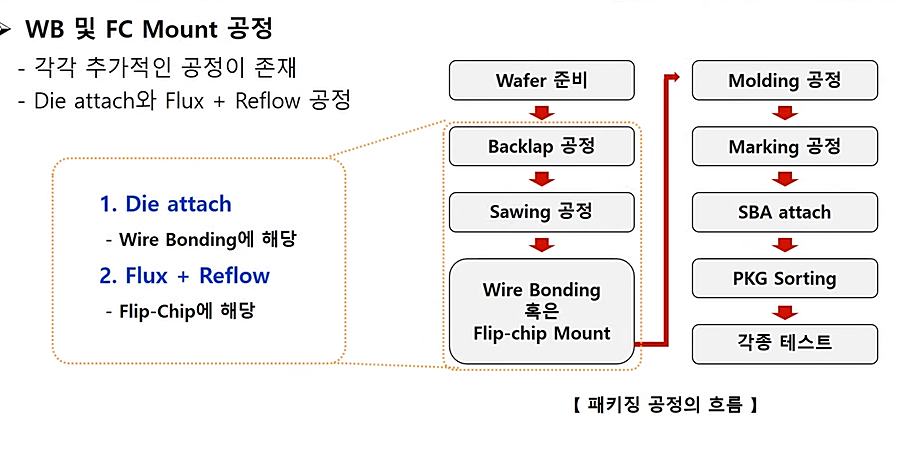

패키징 공정의 흐름

- WAFER 준비

- BACKLAP 공정

- SAWING 공정

- WIRE BONDING 혹은 FLIP-CHIP MOUNT

- MOLDING 공정

- MARKING 공정

- SBA ATTACH 솔더볼 붙임

- PKG SORTING

- 각종 테스트

WB 및 FC MOUNT 공정

- 각각 추가적인 공정이 존재

- DIE ATTACH 와 FLUX+REFLOW 공정

- DIE ATTACH 는 WB에 해당, 후자는 FLIP-CHIP에 해당

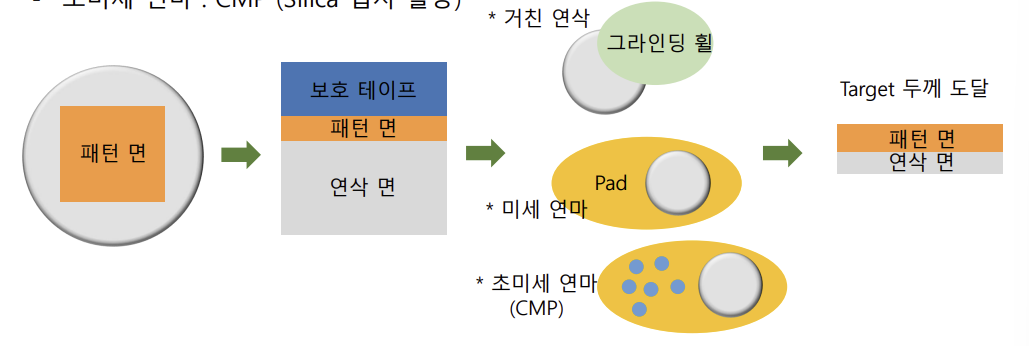

BACKLAP, BACKGRINDING 공정

- 백 그라인딩(Back Grinding, B/G) 공정은 제작된 웨이퍼를 패키지 특성에 적합한 두께로 만들기 위해 웨이퍼의 뒷면을 가공한 후 원형 틀(Ring Frame)에 붙이는(Mount) 공정까지 포함한다.

- 웨이퍼의 뒷면을 연마(Grinding)하기 전, 앞면에 보호용 테이프인 백 그라인딩 테이프를 붙인다

- 이것은 백 그라인딩 공정 중 회로가 구현된 웨이퍼의 앞면에 물리적인 손상이 생기지 않게 하기 위해서다

- 그다음에 휠이 회전하면서 웨이퍼의 뒷면을 연마한다

- 이때, 입자의 크기가 큰 휠을 이용하여 목표 두께 근처까지 빠른 속도로 그라인딩한 뒤, 고운 입자를 가진 휠을 이용하여 목표 두께까지 섬세하게 그라인딩한다

- 그리고 입자가 고운 패드로 표면의 거칠기(Roughness)를 다듬는 폴리싱(Polishing) 작업을 해준다

https://news.skhynix.co.kr/post/seominsuk-column-types-of-packages-6

https://news.skhynix.co.kr/post/seominsuk-column-types-of-packages-6 - 전공정에서 웨이퍼가 입고되면 패턴면과 뒷면이 존재

- 제품의 타겟 두께에 맞게끔 연삭을 진행

- 사포의 원리와 동일하게 거친 연삭 후 미세 연삭 진행

- 메모리는 굉장히 얇게 40UM, 비메모리는 100UM의 두꼐

- GRINDING WHEEL과 PAD 활용

- 초미세 연마: CMP (SILICA 입자 활용) CHEMICAL MECHANICAL POLISHING

- 연삭은 없앤다 연마는 갈아낸다는 차이가 있다

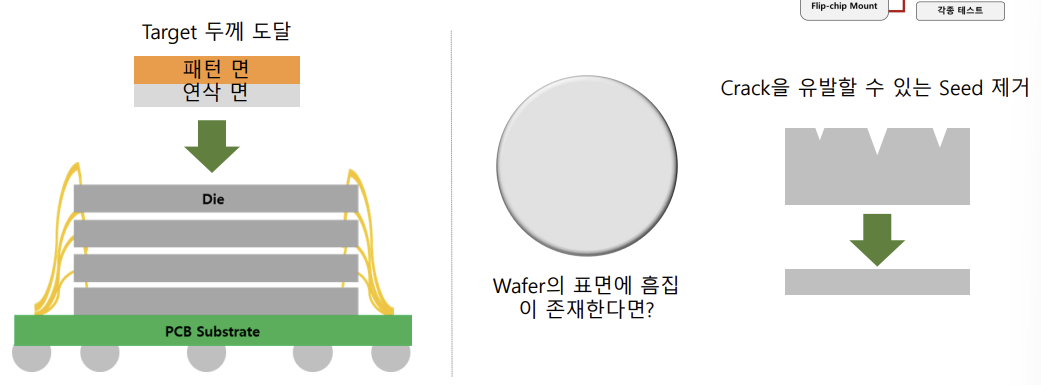

연삭의 이유

- 연삭을 통한 TARGET 두꼐 도달 후 다단 적층 공정

- WAFER에 존재하는 미세 결함을 제거해 CHIP의 강도를 상승시킴

- 웨이퍼의 표면에 흠집이 존재한다면 CRACK을 유발할 수 있어 SEED를 제거한다

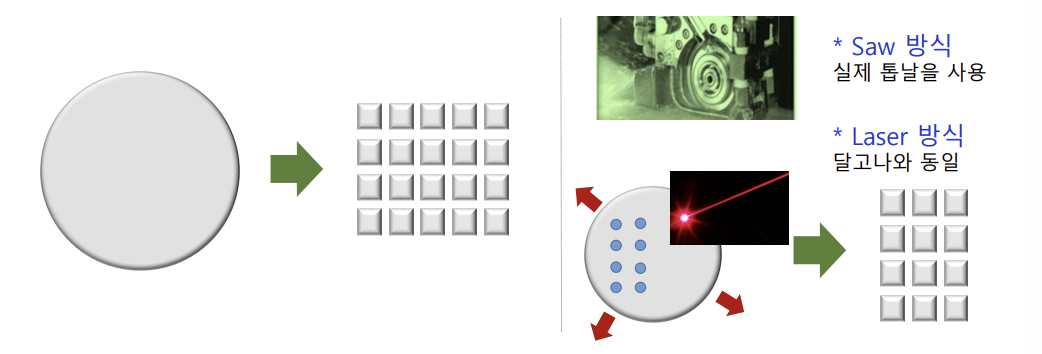

SAWING 공정

- 톱질

- WAFER의 칩들을 개별로 나누는 공정

- SAW 톱의 물리적 방식과 LASER 에너지 방식 존재

- 물리적 방식 : BLADE SAW

- 레이저 방식: CO_2 레이저

- 레이저로 점을 만들고 모든 방향으로 쫙 땡겨주면 깔끔하게 떨어짐

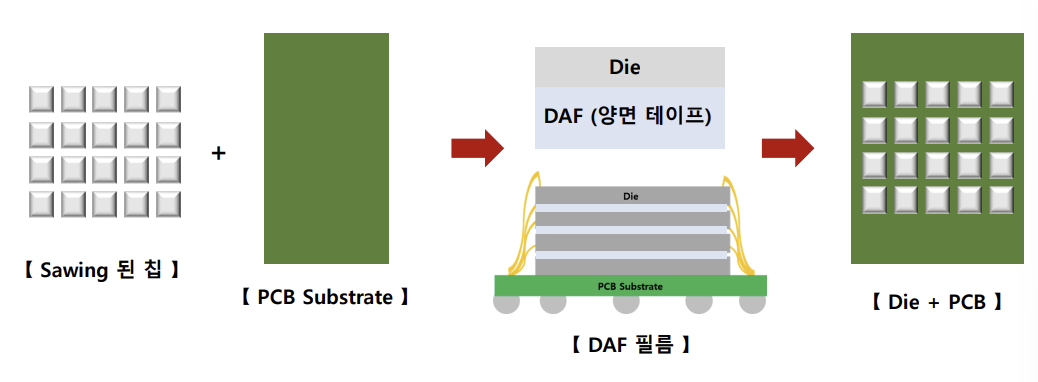

DIE ATTACH 공정 (WIRE BONDING을 위한)

- PCB SUBSTRATE 위에 SAWING된 칩들을 낱개 단위로 놓아줌

- PCB와 DIE 간의 접착을 위해 DIE ATTACH FILM (DAF)이라고 하는 양면 테이프를 사용

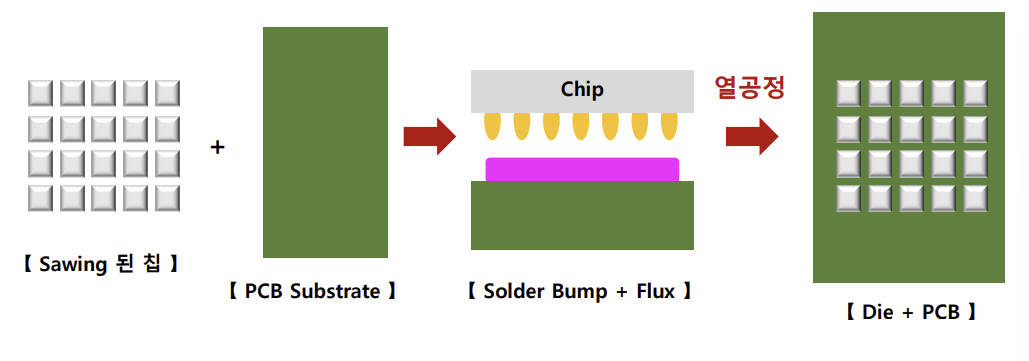

FLIP CHIP MOUNT

- FLIP CHIP 패키지의 경우, 패턴면의 아래쪽에 SOLDER BUMP가 존재

- CHIP의 SOLDER BUMP와 PCB 간의 결합을 위해 FLUX라고 하는 송진과 같은 역할을 하는 화학 약품을 바른 후, 열 공정(REFLOW)를 통해 PCB와 결합을 진행

참고할 글

반도체 기술 탐구: 반도체 패키지 공정 개요

1. 패키지 공정의 필요성 전공정에서 제작된 웨이퍼를 전자기기에 탑재 가능한 형태로 만드는 공정을 의 미한다. 반도체 칩 자체로는 어떤 역할도 할 수가 없다. 반도체가 제기능을 하기 위해서

tristanchoi.tistory.com

반도체 패키징 공정 간략 정리

dynalist.io/d/OKJEfNz2_4A1ohQaq3TCmtN9#inline-images&theme=default 다이날리스트로 정리했는데요. 링크를 누르시면 그림이 있는 버전을 볼 수 있습니다. 12.와이어본딩(패키징기술) - Dynalist dynalist.io 본딩(패키징

coconx.tistory.com

자료 출처

쉽게 이해하는 반도체 패키징 - 반도체 패키징 연구실 (한밭대학교 FCML)

쉽게 이해하는 반도체 패키징

쉽게 이해하는 반도체 패키징 공정 강의 입니다.

www.youtube.com

이어지는 글

컨벤셔널 패키지 제조 공정 2

WIRE BONDING (WB) 공정 DIE ATTACH 공정 이후 GOLD WIRE를 연결하여 DIE와 PCB의 전기적 연결을 진행 GOLD WIRE의 경우 SPARK/초음파를 통해 둥근 공으로 (FREE AIR BALL) 만든 후 접합 DIE의 PAD와 PCB의 LEAD에 순차적으

semi52.tistory.com

어드밴스드 패키지 제조공정 1

ADVANCED PACKAGE - TSV 기술 THROUGH SILICON VIA - TSV 기술: 칩 내부에 직접 관통하는 기술로 빠른 전기적 장점 및 다단구조에도 유리 맨 밑의 DIE, BUFFER DIE에 직접 밖으로 전기를 인출하는 솔더볼(Solder Ball)

semi52.tistory.com

'반도체 > 후공정' 카테고리의 다른 글

| 반도체 패키지의 소재 2 (0) | 2024.02.17 |

|---|---|

| 반도체 패키지의 소재 1 (0) | 2024.02.17 |

| 어드밴스드 패키지 제조공정 1 (0) | 2024.02.17 |

| 컨벤셔널 패키지 제조 공정 2 (0) | 2024.02.17 |

| 반도체 패키지와 테스트 (0) | 2024.02.15 |