ADVANCED PACKAGE 어드밴스드 패키징 - TSV 기술

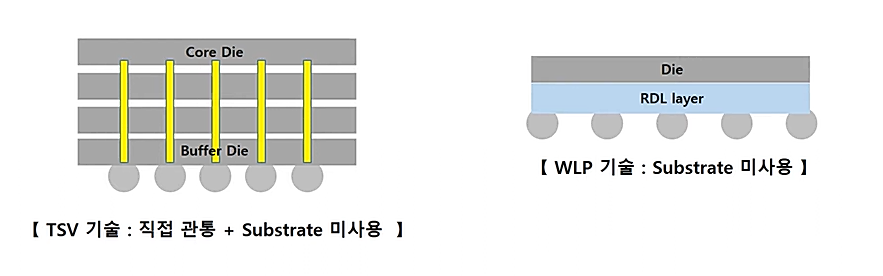

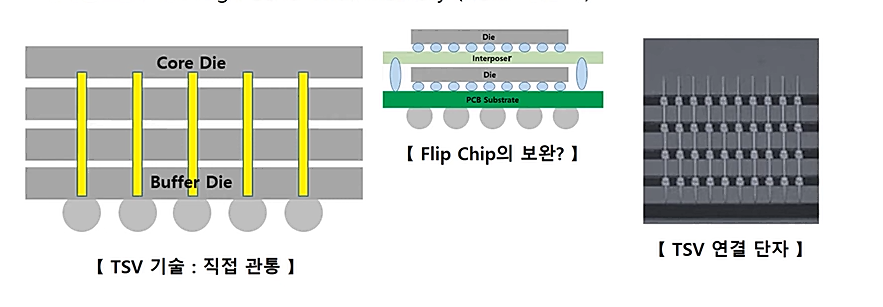

- THROUGH SILICON VIA - TSV 기술: 칩 내부에 직접 관통하는 기술로 빠른 전기적 장점 및 다단구조에도 유리

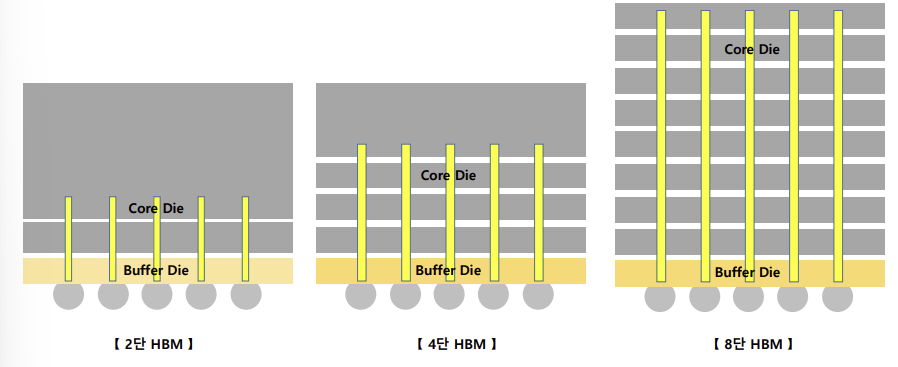

- 맨 밑의 DIE, BUFFER DIE에 직접 밖으로 전기를 인출하는 솔더볼(Solder Ball)을 연결

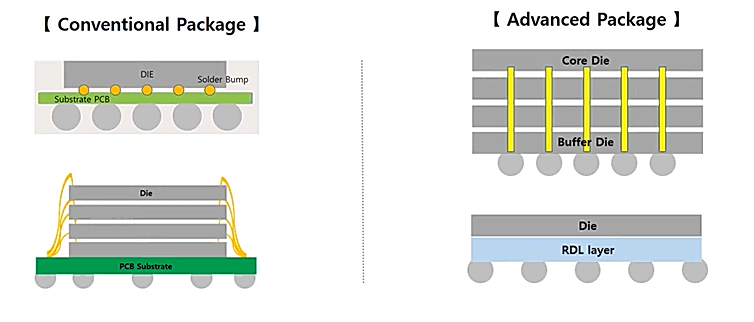

- WAFER LEVEL PACKAGE (WLP): PCB 기판을 사용하지 않고 바로 DIE에 전기적 배선을 만들어버리는 기술로 다단 적층에도 장점이 생김

- RDL LAYER가 PCB를 대체하기 때문에 공정 난이도 상승, 대량 생산 힘듬

- 전기적으로 빠르게 작동, 단가만 낮춰진다면 상용화 가능성 매우 높음

TSV (Through Silicon Via)란?

- Through Silicon Via, 실리콘 관통전극

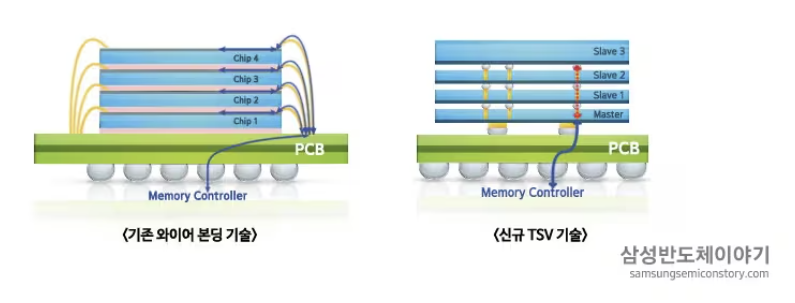

- 기존 와이어를 이용해 칩을 연결하는 대신 칩에 미세한 구멍을 뚫어 상단 칩과 하단 칩을 전극으로 연결하는 D램 칩을 일반 종이 두께의 절반보다도 얇게 깎은 후, 미세한 구멍을 뚫어 칩 상하단의 구멍을 전극으로 연결하는 패키징 기술이다

- TSV는 메모리 칩을 적층해 대용량을 구현하는 기술로, 기존 금선(와이어)을 이용해 칩을 연결하는 와이어 본딩(Wire Bonding) 기술보다 속도와 소비전력을 크게 개선할 수 있는 것이 특징이다

- 삼성전자는 2010년 세계 최초로 TSV 기반 D램 모듈을 개발한 데 이어, 2014년 8월 세계 최초로 3차원 TSV 적층 기술을 적용한 64GB 차세대 DDR4 서버용 D램 모듈 양산을 발표했다.

- 출처: https://semiconductor.samsung.com/kr/support/tools-resources/dictionary/semiconductor-glossary-tsv/

https://news.skhynix.co.kr/post/wafer-level-package-technical-manager - TSV(Through Silicon Via, 실리콘 관통 전극)는 칩과 칩을 수직으로 관통하는 전극에 범프(Bump)를 형성한 후 여러 개의 칩을 적층하는 기술을 뜻한다

- 칩을 수직 연결해 전기적 연결 통로의 길이를 줄임으로써, 속도를 향상시키고 소비전력을 개선할 수 있다

- 적층되는 칩의 개수에 따라 용량이 늘어나 고용량을 구현하기가 용이하다는 장점도 있다.

- 출처: https://news.skhynix.co.kr/post/wafer-level-package-technical-manager

웨이퍼 레벨 패키지란?

- WLP는 웨이퍼를 칩 단위로 잘라 칩을 패키지 공정하는 기존의 컨벤셔널 패키지(Conventional Package)에서 한 단계 발전한 방식으로, 웨이퍼 상(Wafer Level)에서 패키징(Packaging)을 마무리해 완제품을 만드는 기술을 의미한다

- WLP는 웨이퍼를 먼저 칩으로 자르고 이를 기판에 올려 전기적으로 연결한 뒤, 몰딩(Molding) 작업을 진행해 하나의 제품으로 완성하는 기존 컨벤셔널 패키지 방식과 달리, 웨이퍼 레벨에서 전기적 연결과 몰딩 작업까지 완료한 후 칩으로 자르는 방식이다. 칩 크기 그대로 패키징할 수 있어 초소형 제품을 만드는 데 유리하며, 기판이나 와이어 같은 재료를 사용하지 않아 원가를 절감할 수 있다는 장점이 있다.

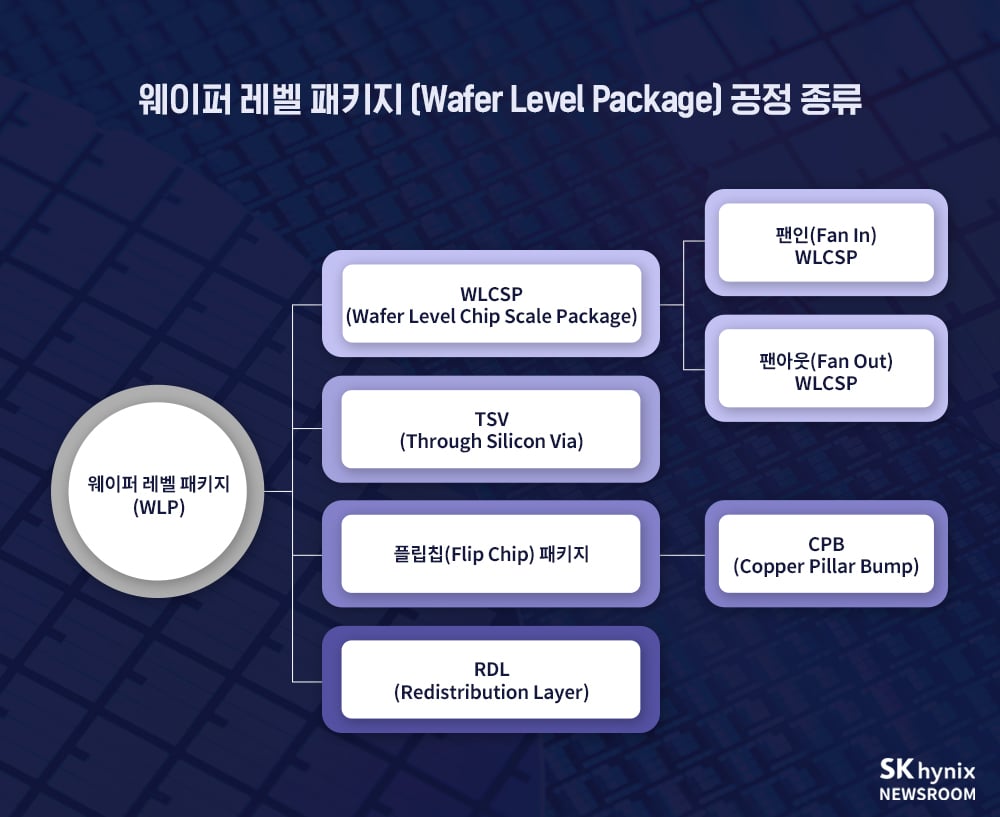

https://news.skhynix.co.kr/post/wafer-level-package-technical-manager - 대표적으로 전체 공정을 웨이퍼 상태에서 진행하는 팬인(Fan in) WLCSP(Wafer Level Chip Scale Package), 팬아웃(Fan out) WLCSP가 있다

- 전체 패키지 공정의 일부를 웨이퍼 상태로 진행하는 RDL(ReDistribution Layer) 패키지, 플립 칩(Flip Chip) 패키지, TSV 패키지도 넓은 의미에서는 웨이퍼 레벨 패키지 범주에 들어간다

팬인과 팬아웃의 차이

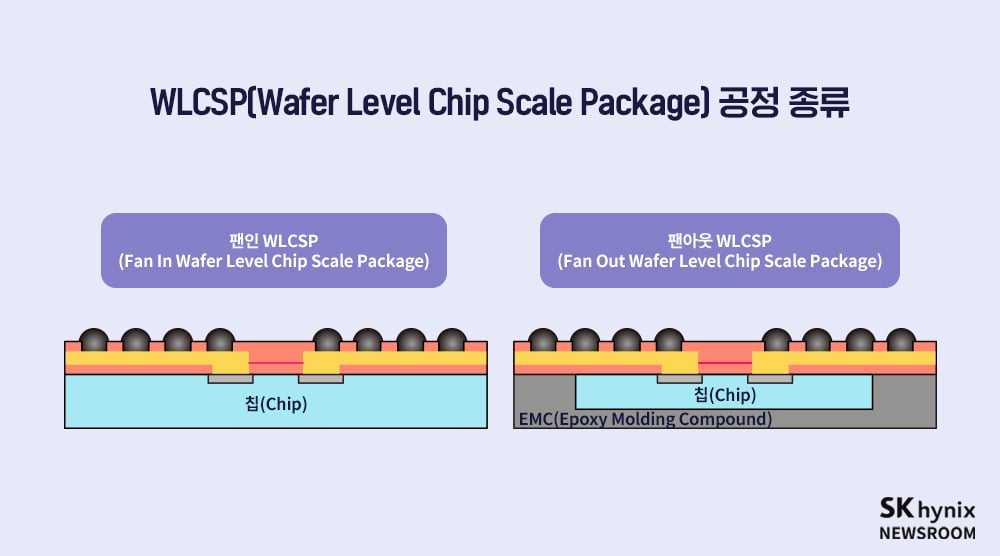

- 패키지 공정 전체를 웨이퍼 레벨에서 진행하는 WLCSP(Wafer Level Chip Scale Package)는 패키지용 배선, 절연층, 솔더볼(Solder Ball, 입출력 단자를 웨이퍼 바로 위에 붙이는 방식의 기술로, 팬(Fan, 칩의 크기를 의미)의 타입에 따라 ‘팬인(Fan In) WLCSP’과 ‘팬아웃(Fan Out) WLCSP’로 다시 구분된다

- 칩 크기가 패키지 크기와 같고 칩 내 솔더볼이 구현된 것이 팬인(Fan In)

- 칩보다 패키지 크기가 크고 솔더볼이 칩 밖에도 구현된 것이 팬아웃(Fan Out)이다

- 두 기술 모두 기판과 같은 매개체 없이 솔더볼을 칩 위에 바로 붙여 패키징하는 방식으로, 배선의 길이가 줄어든 만큼 전기적 특성이 향상되거나 패키지 두께가 얇아져 칩을 더 많이 적층할 수 있다

- 출처: https://news.skhynix.co.kr/post/wafer-level-package-technical-manager

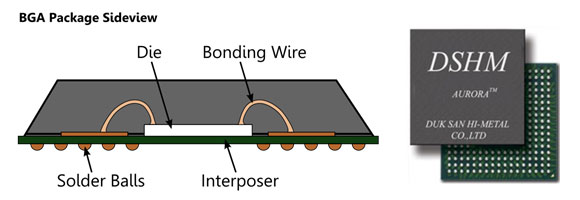

솔더볼이란?

솔더볼은 BGA(Ball Grid Array), CSP(Chip Scale Package) 와 같은 반도체 패키지 기술의 핵심 부품으로, 칩과 기판을 연결하여 전기적 신호를 전달하는 역할을 하는 기술 집약적인 제품이다.

출처: 덕산하이메탈(주)

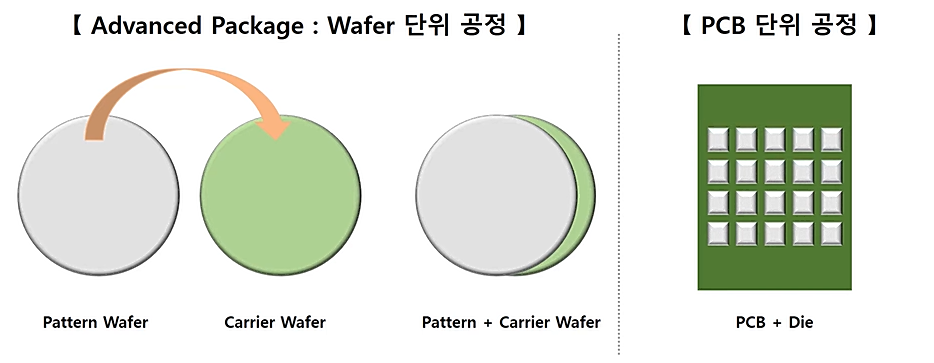

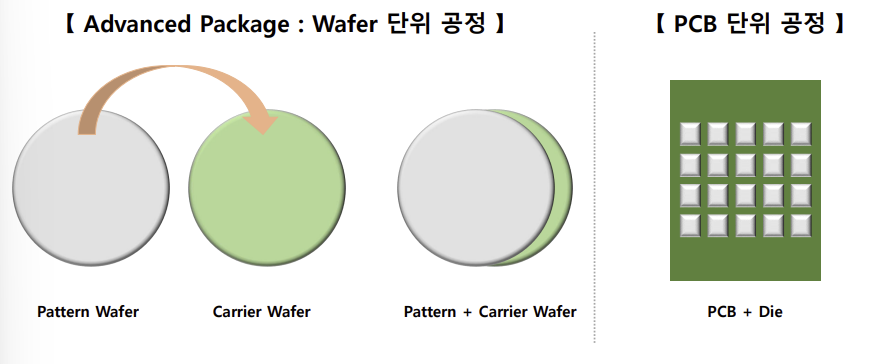

CARRIER WAFER

- TSV 혹은 WLP 공정을 위해 사용되는 공정용 (운반용) 웨이퍼 (혹은 유리)

TSV 기술 (THROUGH SILICON VIA)

- TSV 기술의 가장 큰 장점은 빠른 전기 인출에 있으며, 서버용 메모리와 같이 고성능용 메모리 제품을 만드는데 사용

- 서버용 메모리: HIGH BAND WIDTH MEMORY - HBM 메모리

- 빠른 전기적 인출이 가능한 메모리의 필요성이 부상

어드밴스드 패키징을 견인하는 인터커넥션 기술의 가치와 SK하이닉스 패키징 기술 혁신

어드밴스드 패키징의 핵심은 패키징에서의 연결 즉, ‘패키징 인터커넥션(Interconnection)’ 기술이다. 이 글에서는 패키징 기술의 진화와 이에 기여하고 있는 SK하이닉스의 기술력 및 성과를 다뤄

news.skhynix.co.kr

SK하이닉스 뉴스룸 기획 콘텐츠

SK하이닉스는 반도체 기술 기반의 IT 생태계 리더로서 사회 구성원 모두와 함께 더 나은 세상을 만듭니다. 다양한 반도체 기술과 트렌드를 SK하이닉스 뉴스룸에서 만나세요.

news.skhynix.co.kr

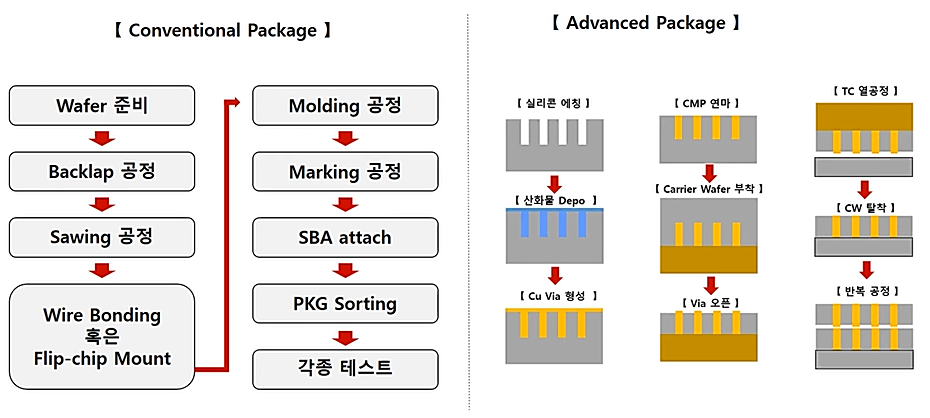

ADVANCED VS CONVENTIONAL PACKAGE

장점과 단점 TRADE-OFF

- CONVENTIONAL PACKAGING이 생산성이 용이하고 단가가 낮음, 특히 와이어본딩

- ADVANCED PACKAGE는 성능적인 측면에서 매우 향상되나 작업성과 비용적 측면에서 손해

- PCB 사용 안하고 웨이퍼 단위에서 공정을 진행하므로 수율적인 측면에서 장점

- 결국 기술적 발전은 더 빠른 용량과 성능을 요구하므로 ADVANCED PACKAGE 방향으로 나아가고 있다

공정 차이

CONVENTIONAL PACKAGE

- WAFER 준비

- BACKLAP 공정

- SAWING 공정

- WIRE BONDING 혹은 FLIP CHIP MOUNT

- MOLDING 공정

- MARKING 공정

- SBA ATTACH 솔더볼 붙임

- PKG SORTING

- 각종 테스트

ADVANCED PACKAGE

- 직접 웨이퍼에 전기적 배선

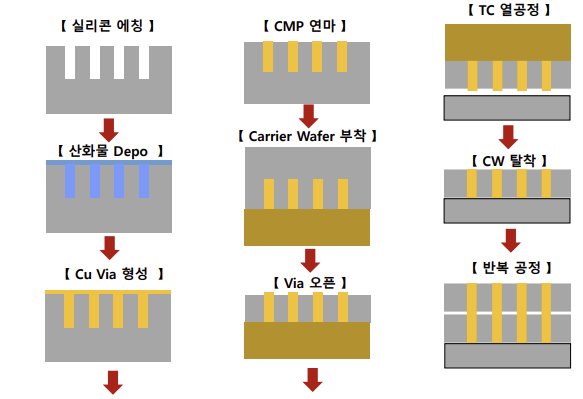

- 실리콘 에칭

- 산화물 DEPO

- CU VIA 형성

- CMP 연마

- CARRIER WAFER 부착

- VIA 오픈

- TC 열공정

- CW 탈착

- 반복 공정

AVP 제조공정

ADVANCED PACKAGE (진화된 패키징 방식)

- THROUGH SILICON VIA 기술 (TSV) : CHIP 내부에 직접 관통하는 기술로 빠른 전기적 장점 및 다단구조에도 유리

- WAFER LEVEL PACKAGE (WLP) : PCB SUBSTRATE를 사용하지 않고 바로 DIE에 전기적 배선을 만들어 버리는 기술 다단 적층에도 장점이 생김

- WAFER 단위로 공정이 이루어짐

TSV 기술

- WAFER에 TSV를 형성한 후 연삭 등의 공정을 거친 후 겹겹이 쌓는 방식으로 진행된다.

공정 순서

- 실리콘 에칭

- 산화물 DEPO

- CU VIA 형성

- CMP 연마

- CARRIER WAFER 부착

- VIA 오픈

- TC 열공정 (THERMAL COMPRESSION)

- CW 탈착

- 반복 공정

CARRIER WAFER

- TSV 혹은 WLP 공정을 위해 사용되는 공정용 (운반용) 웨이퍼 (혹은 유리)

- PCB 단위 공정 -> WAFER 단위 공정 - ADVANCED PACKAGE

TSV 다단 기술

- 2단, 4단, 8단 등으로 제조가 가능하며, 패키지의 높이는 대부분 비슷하게 제조하며 가장 위쪽 DIE의 연삭 높이를 다르게 함

- BUFFER DIE가 맨 밑에서 PCB의 역할을 함

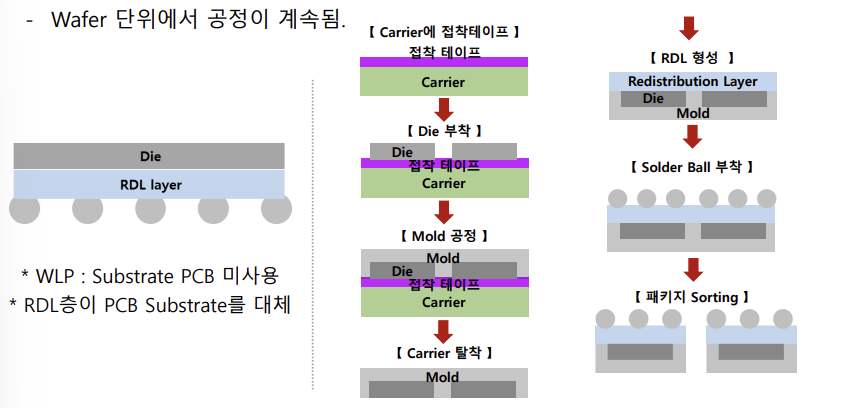

WAFER LEVEL PACKAGE

- WLP에서 가장 중요한 것은 PCB SUBSTRATE를 대체하는 RDL층을 형성하는 공정이다.

- WAFER 단위에서 공정이 계속됨

- CARRIER에 접착테이프 -> DIE 부착 -> MOLD 공정 -> CARRIER 탈착 -> RDL 형성 -> SOLDER BALL 부착 -> 패키지 SORTING

공정 난이도 및 단가 차이

- CONVENTIONAL PACKAGE 공정 난이도가 상대적으로 낮으며, 대량 생산에 유리

- 대량 생산의 유리하기 때문에 단가의 차이가 발생함

- FLIP CHIP보다 TSV가 공정난이도 높음

- WB에서 WLP로 전환되는 추세

- 기술이 발전한다면 PCB로 옮기지 않고 웨이퍼 단위에서 바로 할 수 있기 때문에 WLP의 중요성은 상승 추세

참고할 글

반도체 차세대 패키지 모음집

패키지개발 엔지니어가 되고 싶은 취준생의 일상 정리

자료 출처

쉽게 이해하는 반도체 패키징 - 반도체 패키징 연구실 (한밭대학교 FCML)

쉽게 이해하는 반도체 패키징

쉽게 이해하는 반도체 패키징 공정 강의 입니다.

www.youtube.com

이어지는 글

컨벤셔널 패키지 제조 공정 1

패키징의 정의 외부환경으로부터 보호하고 단자간 연결을 위한 전기적인 포장. 반도체 칩을 탑재될 기기에 적합한 형태로 포장한다 PCB - Printed Circuit Board (인쇄 회로 기판) 컴퓨터를 열어보았을

semi52.tistory.com

'반도체 > 후공정' 카테고리의 다른 글

| 반도체 패키지의 소재 2 (0) | 2024.02.17 |

|---|---|

| 반도체 패키지의 소재 1 (0) | 2024.02.17 |

| 컨벤셔널 패키지 제조 공정 2 (0) | 2024.02.17 |

| 컨벤셔널 패키지 제조 공정 1 (0) | 2024.02.16 |

| 반도체 패키지와 테스트 (0) | 2024.02.15 |