Through-silicon via

https://www.youtube.com/watch?v=s5IBdqM07P8&pp=ygUTVGhyb3VnaC1zaWxpY29uIHZpYQ%3D%3D

Through-silicon via - Wikipedia

전자 공학에서 실리콘 관통 비아(TSV, through-silicon via) 또는 칩 관통 비아는 실리콘 웨이퍼 또는 다이를 완전히 관통하는 수직 전기 연결(비아)이다. TSV는 와이어 본드와 플립 칩을 대체하는 고성능 상호 연결 기술로 사용되어 3D 패키지와 3D 집적 회로를 만드는데 활용된다. 패키지-온-패키지와 같은 대안에 비해 상호 연결 및 장치 밀도가 크게 높아지고 연결 길이도 짧아진다.

Classification

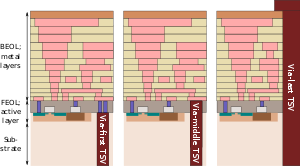

제조 공정에 따라 세 가지 유형의 TSV가 존재한다. via-first TSV는 개별 구성 요소(트랜지스터, 커패시터, 저항기 등)가 패턴화되기 전에 제작되며, via-middle TSV는 개별 구성 요소가 패턴화된 후 금속 층(후면 공정)이 형성되기 전에 제작되고, via-last TSV는 후면 공정 중 또는 후에 제작된다. 중간 비아 TSV는 현재 고급 3D IC 및 중간층 스택에 널리 사용되고 있다.

전면 공정(FEOL) 단계의 TSV는 EDA와 제조 단계에서 주의 깊게 고려되어야 한다. 그 이유는 TSV가 FEOL 층에 열역학적 응력을 유발하여 트랜지스터 특성에 영향을 미치기 때문이다.

CMOS 이미지 센서(CIS)는 대량 생산에서 TSV를 도입한 최초의 응용 분야이다. 초기 CIS 응용에서는 TSV가 이미지 센서 웨이퍼의 후면에 형성되어 상호 연결부를 만들고 와이어 본드를 없애며 폼 팩터를 줄이고 고밀도 상호 연결을 가능하게 했다. 칩 적층은 후면 조명 CIS의 등장과 함께 시작되었는데, 렌즈, 회로, 포토다이오드의 순서를 전면 조명과 반대로 뒤집는 것으로 이루어졌다. 이를 위해 포토다이오드 웨이퍼를 뒤집고 후면을 얇게 만든 뒤 직접 산화 본딩으로 판독 층 위에 붙였고, 주변부에 TSV를 사용했다.

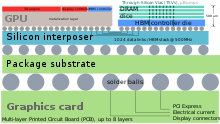

3D 패키지(시스템 인 패키지, 칩 스택 MCM 등)는 두 개 이상의 칩(집적 회로)을 수직으로 쌓아 공간을 적게 차지하고/또는 더 많은 연결성을 가지게 한다. IBM의 실리콘 캐리어 패키징 기술에서 찾을 수 있는 다른 유형의 3D 패키지에서는 칩이 적층되지 않고 TSV가 포함된 캐리어 기판을 사용하여 여러 IC를 패키지에 연결한다. 대부분의 3D 패키지에서 적층된 칩은 가장자리를 따라 연결되는데, 이 가장자리 배선은 패키지의 길이와 너비를 약간 증가시키고 보통 칩 사이에 추가 "중간층"이 필요하다. 일부 새로운 3D 패키지에서는 TSV가 가장자리 배선을 대체하여 칩 본체를 통해 수직 연결을 만든다. 그 결과 패키지 길이나 너비가 늘어나지 않으며 중간층도 필요하지 않아 더 납작해질 수 있다. 이 TSV 기술은 때로 TSS(Through-Silicon Stacking 또는 Thru-Silicon Stacking)라고도 불린다.

https://www.youtube.com/watch?v=QxrpjCDkAmk&pp=ygUTVGhyb3VnaC1zaWxpY29uIHZpYQ%3D%3D

Applications

Image sensors

CMOS 이미지 센서(CIS)는 대량 생산에서 TSV를 도입한 최초의 응용 분야이다. 초기 CIS 응용에서는 TSV가 이미지 센서 웨이퍼의 후면에 형성되어 상호 연결부를 만들고 와이어 본드를 없애며 폼 팩터를 줄이고 고밀도 상호 연결을 가능하게 했다. 칩 적층은 후면 조명 CIS의 등장과 함께 시작되었는데, 렌즈, 회로, 포토다이오드의 순서를 전면 조명과 반대로 뒤집는 것으로 이루어졌다. 이를 위해 포토다이오드 웨이퍼를 뒤집고 후면을 얇게 만든 뒤 직접 산화 본딩으로 판독 층 위에 붙였고, 주변부에 TSV를 사용했다.

3D packages

3D 패키지(시스템 인 패키지, 칩 스택 MCM 등)는 두 개 이상의 칩(집적 회로)을 수직으로 쌓아 공간을 적게 차지하고/또는 더 많은 연결성을 가지게 한다. IBM의 실리콘 캐리어 패키징 기술에서 찾을 수 있는 다른 유형의 3D 패키지에서는 칩이 적층되지 않고 TSV가 포함된 캐리어 기판을 사용하여 여러 IC를 패키지에 연결한다. 대부분의 3D 패키지에서 적층된 칩은 가장자리를 따라 연결되는데, 이 가장자리 배선은 패키지의 길이와 너비를 약간 증가시키고 보통 칩 사이에 추가 "중간층"이 필요하다. 일부 새로운 3D 패키지에서는 TSV가 가장자리 배선을 대체하여 칩 본체를 통해 수직 연결을 만든다. 그 결과 패키지 길이나 너비가 늘어나지 않으며 중간층도 필요하지 않아 더 납작해질 수 있다. 이 TSV 기술은 때로 TSS(Through-Silicon Stacking 또는 Thru-Silicon Stacking)라고도 불린다.

3D integrated circuits

3D 집적 회로(3D IC)는 실리콘 웨이퍼 및/또는 다이를 수직으로 쌓아 상호 연결하여 단일 장치로 작동하게 만든 단일 집적 회로이다. TSV 기술을 사용하여 3D IC는 작은 "영역"에 많은 기능을 집약할 수 있다. 적층된 다양한 장치들은 CMOS 논리, DRAM, III-V 소재 등 이질적인 것일 수 있다. 또한 장치를 통한 핵심 전기 경로를 크게 단축할 수 있어 더 빠른 작동이 가능하다. 와이드 I/O 3D DRAM 메모리 표준(JEDEC JESD229)에도 TSV가 포함되어 있다.

https://www.youtube.com/watch?v=vTfGHkdp8i0&pp=ygUTVGhyb3VnaC1zaWxpY29uIHZpYQ%3D%3D

History

TSV 개념의 기원은 1958년에 출원되어 1962년에 등록된 윌리엄 쇼클리의 특허 "Semiconductive Wafer and Method of Making the Same"로 거슬러 올라간다. 이후 IBM 연구원들인 멀린 스미스와 이매뉴얼 스턴이 1964년에 출원하고 1967년에 등록된 특허 "Methods of Making Thru-Connections in Semiconductor Wafers"에서 실리콘 관통 홀 제작 방법을 더 발전시켰다. TSV는 처음에 3D 집적을 위해 설계된 것이 아니었지만, 1980년대에 들어 TSV 기반의 최초 3D 칩이 발명되었다.

1980년대 일본에서 TSV 공정으로 제작된 최초의 3D 집적 회로(3D IC) 적층 칩이 발명되었다. 히타치가 1983년, 후지쯔가 1984년에 일본 특허를 출원했고, 1986년 후지쯔는 TSV를 사용한 적층 칩 구조에 대한 일본 특허를 출원했다. 1989년 도호쿠 대학의 코요나기 미쓰마사 교수는 TSV와 웨이퍼 본딩 기술을 사용해 3D LSI 칩을 제작했다. 1999년 일본의 차세대 전자 기술 연구조합(ASET)이 TSV 기술을 이용한 3D IC 칩 개발을 지원하기 시작했고, 도호쿠 대학 코요나기 연구팀은 1999년부터 TSV 기술로 다양한 적층 칩을 제작했다.

2000년대에 들어 전자 산업계의 TSV 기술에 대한 관심이 크게 높아졌다. 2004년 국제 반도체 기술 로드맵(ITRS)에서 TSV 기술의 3D IC 응용 잠재력이 강조되었고, 이는 산업 전반의 TSV 기반 3D IC와 3D 패키지 개발 활동을 촉발시켰다. IBM, 삼성전자, GlobalFoundries, Intel, Micron, SK하이닉스, TSMC 등 주요 반도체 제조업체들이 TSV 기술 개발과 연구 결과를 활발히 발표했다.

2000년대 초반부터 TSV 기술은 다양한 상용 제품 개발을 가능하게 했다. 여기에는 3D 이미지 센서, 3D DRAM, 3D 논리/메모리 적층 칩, 중간층 기반 SiP(시스템 인 패키지) 제품 등이 포함된다. 주요 상업적 동인은 모바일폰 카메라 모듈, 고성능 컴퓨팅을 위한 고대역폭 메모리, 그리고 작은 영역에서의 이질적 기능 통합 등이었다. 지난 10년간 TSV 기술은 진화하며 널리 채택되어 왔고, 업계 주도로 많은 투자와 돌파구가 보고되었다.

현재 TSV 기술은 첨단 3D IC와 3D 패키징 솔루션을 가능하게 하는 핵심 기술이며, 향후 반도체 소자의 지속적인 스케일링과 집적에 점점 더 중요한 역할을 할 것으로 예상된다.

도호쿠 대학 코요나기 연구팀은 TSV 기술로 1999년 3층 적층 이미지 센서 칩, 2000년 3층 메모리 칩, 2001년 3층 인공 망막 칩, 2002년 3층 마이크로프로세서, 2005년 10층 메모리 칩을 제작했다.

1997년 프라운호퍼-지멘스 연구팀은 ICV(inter-chip via) 방식을 개발했는데, 이는 TSV 공정의 변형으로 나중에 SLID(solid liquid inter-diffusion) 기술로 불리게 되었다.

https://www.youtube.com/watch?v=aCOyq4YzBtY&pp=ygUTVGhyb3VnaC1zaWxpY29uIHZpYQ%3D%3D

"through-silicon via"(TSV)라는 용어는 Tru-Si Technologies의 연구진 Sergey Savastiouk, O. Siniaguine, E. Korczynski가 2000년에 3D 웨이퍼 레벨 패키징(WLP) 솔루션을 위한 TSV 방식을 제안하면서 만들어졌다.

도시바, 아프티나, STMicroelectronics 등이 2007-2008년 사이 TSV를 활용한 CMOS 이미지 센서를 상용화했고, 도시바는 자사 기술을 "Through Chip Via"(TCV)로 명명했다. 엘피다 메모리는 2009년 9월 4개의 DDR3 SDRAM 다이로 쌓은 최초의 8GB DRAM 칩을 개발했고 2011년 6월 출시했다. TSMC는 2010년 1월 TSV 기술을 이용한 3D IC 생산 계획을 발표했다. 2011년 SK하이닉스는 TSV 기술을 사용한 16GB DDR3 SDRAM(40nm급)을, 삼성전자는 TSV 기반 32GB DDR3(30nm급)을 발표했으며 삼성과 마이크론은 TSV 기반 하이브리드 메모리 큐브(HMC) 기술을 발표했다. SK하이닉스는 2013년 TSV 기술 기반의 최초 하이브리드 메모리(HBM) 칩을 제조했다.

중간 비아(via middle) 기술은 Eric Beyne가 주도한 imec에 의해 개발되었는데, 비용과 상호 연결 밀도 측면에서 최적의 절충안을 제공했다. 이 연구는 퀄컴, 나중에는 엔비디아, 자일링스, 알터라의 지원을 받았는데, 이들은 칩 내 메모리를 늘리되 스케일링이 아닌 적층 방식으로 Intel을 능가하고자 했다.

https://www.youtube.com/watch?v=KSazZVHfP8U&pp=ygUTVGhyb3VnaC1zaWxpY29uIHZpYQ%3D%3D

'반도체 > 후공정' 카테고리의 다른 글

| [📚세미피디아] Interposer, 인터포저란? (0) | 2024.04.14 |

|---|---|

| [📚세미피디아] 칩렛, 멀티칩 모듈이란? (0) | 2024.04.13 |

| 반도체 패키지의 소재 2 (0) | 2024.02.17 |

| 반도체 패키지의 소재 1 (0) | 2024.02.17 |

| 어드밴스드 패키지 제조공정 1 (0) | 2024.02.17 |