Charge trap flash

https://en.wikipedia.org/wiki/Charge_trap_flash

https://www.youtube.com/watch?v=oQxV-q66STo&pp=ygURQ2hhcmdlIHRyYXAgZmxhc2g%3D

전하 트랩 플래시(CTF)는 불휘발성 NOR 및 NAND 플래시 메모리를 만드는 데 사용되는 반도체 메모리 기술이다. 이는 전통적인 플로팅 게이트 기술과는 다른 부동 게이트 MOSFET 메모리 기술의 일종이며, 전하를 저장하기 위해 도핑된 다결정 실리콘 대신 실리콘 나이트라이드 필름을 사용한다. 이러한 접근 방식을 통해 메모리 제조업체는 다음의 5가지 방법으로 제조 비용을 줄일 수 있다:

- 전하 저장 노드를 형성하는 데 필요한 공정 단계가 더 적다.

- 더 작은 공정 크기를 사용할 수 있다(따라서 칩 크기와 비용을 줄일 수 있다).

- 단일 플래시 메모리 셀에 다중 비트를 저장할 수 있다.

- 신뢰성이 향상된다.

- 터널 산화물 층의 점결함에 더 취약하지 않기 때문에 수율이 높다.

전하 트랩 개념은 이전부터 있었지만, 2002년에 AMD와 Fujitsu가 고용량 전하 트래핑 플래시 메모리를 본격적으로 생산하기 시작했다. 이들은 GL NOR 플래시 메모리 제품군 출시로 전하 트래핑 플래시 메모리의 상업적 생산을 시작했다. 현재 스판션 명으로 운영되는 이 기업은 이때부터 계속해서 전하 트래핑 장치를 대량으로 생산해왔다. 2008년 2,500억 달러 규모의 NOR 플래시 시장에서 전하 트래핑 플래시가 30%를 차지했다. 여러 기업에게 대규모 전하 트래핑 기술 포트폴리오를 라이선스했던 Saifun Semiconductors는 2008년 3월 스판션에 인수되었다. 2000년대 후반부터 CTF는 도시바와 삼성전자가 개발한 3D V-NAND 플래시 메모리의 핵심 구성 요소가 되었다.

https://www.youtube.com/watch?v=DfaA1hgABrc&pp=ygURQ2hhcmdlIHRyYXAgZmxhc2g%3D

기원

금속-산화물-반도체 전계 효과 트랜지스터(MOSFET) 또는 MOS 트랜지스터는 1959년 이집트 출신 엔지니어 Mohamed M. Atalla와 한국계 엔지니어 Dawon Kahng이 벨 연구소에서 발명했으며, 1960년에 이를 시연했다. Kahng은 이후 벨 연구소에서 Simon Min Sze와 함께 부동 게이트 MOSFET을 발명했고, 이를 부동 게이트(FG) 메모리 셀로 사용할 것을 제안했다. 이것은 부동 게이트 MOSFET에 전하를 주입하고 저장함으로써 구현된 최초의 불휘발성 메모리 형태였으며, 이후 EPROM(소거 가능 PROM), EEPROM(전기적 소거 가능 PROM) 및 플래시 메모리 기술의 기반이 되었다.

전하 트래핑 개념은 1967년 John Szedon과 Ting L. Chu에 의해 처음 소개되었다.

1967년 말, H.A. Richard Wegener가 이끄는 Sperry 연구팀은 금속-질화물-산화물-반도체 트랜지스터(MNOS 트랜지스터)를 발명했다. MNOS 트랜지스터는 산화물 층을 질화물과 산화물로 이루어진 이중 층으로 대체한 MOSFET의 일종이다. 질화물은 부동 게이트 대신 트래핑 층으로 사용되었지만, 부동 게이트에 비해 성능이 떨어지는 것으로 여겨져 그 사용이 제한적이었다. MNOS 트랜지스터 소자는 게이트와 채널 간에 50V의 순방향 또는 역방향 바이어스를 인가하여 트랜지스터의 문턱 전압에 영향을 미치는 전하를 포획할 수 있었다.

전하 트랩(CT) 메모리는 1960년대 말 MNOS 소자와 함께 소개되었다. 구조와 작동 원리가 부동 게이트(FG) 메모리와 유사하지만, FG 메모리에서는 전하가 도핑된 다결정 실리콘 층과 같은 도전성 물질에 저장되는 반면, CT 메모리에서는 유전체 층(일반적으로 실리콘 질화물로 제작)의 국부적인 트랩에 전하가 저장된다는 점이 주된 차이이다.

전하 트랩 EEPROM

1974년까지 전하 트랩 기술은 전기적으로 소거 가능한 프로그래밍 가능 읽기 전용 메모리(EEPROM)의 저장 메커니즘으로 사용되었으며, 표준 부동 게이트 MOSFET 기술의 대안이었다. 1977년 페어차일드 카메라 앤 인스트루먼트의 P.C.Y. Chen은 프로그래밍 및 소거 조건이 훨씬 덜 까다롭고 전하 저장 시간이 긴 SONOS라는 MOSFET 기술을 발명했음을 설명하는 논문을 발표했다. 이러한 개선으로 1980년대에 전하 트래핑 SONOS 기반의 제조 가능한 EEPROM 장치가 만들어졌다.

https://www.youtube.com/watch?v=jboZVXi8rQg&pp=ygURQ2hhcmdlIHRyYXAgZmxhc2g%3D

전하 트랩 플래시 실험

1991년 일본의 NEC 연구원들인 N. Kodama, K. Oyama, Hiroki Shirai 등이 전하 트랩 방식을 채택한 플래시 메모리를 개발했다. 1998년 이스라엘 엔지니어 Boaz Eitan은 스판션(당시 사이펀 반도체)에서 전하 트랩 층을 사용하여 기존 플래시 메모리 설계의 부동 게이트를 대체한 NROM 플래시 메모리 기술을 특허 출원했다. 이 특허에는 두 가지 중요한 혁신이 담겨 있다: 주입된 부/정 전하를 셀의 드레인/소스 단자 근처에 국소화하는 것과, 역방향 읽기 개념을 활용하여 셀에 저장된 데이터를 양쪽 끝의 전하 트랩에서 감지하는 것이다. 이 두 가지 새로운 아이디어를 통해 전하 트래핑 개념이 발명된 지 30년 만에 처음으로 신뢰할 수 있는 전하 트랩 플래시 제품을 생산할 수 있게 되었다. 또한 이러한 개념을 활용하면 셀당 두 개의 별도 물리적 비트를 만들어 셀당 저장 데이터의 용량을 두 배로 늘릴 수 있다.

2000년 어드밴스드 마이크로 디바이시스(AMD)의 연구팀, 즉 Richard M. Fastow, 이집트 출신 엔지니어 Khaled Z. Ahmed, 요르단 출신 엔지니어 Sameer Haddad(이후 스판션에 합류)가 NOR 플래시 메모리 셀을 위한 전하 트랩 메커니즘을 시연했다. 이러한 혁신은 AMD와 후지쓰에서 2002년에 더욱 발전되었고(이후 스판션에 의해 개선), 이들 기업들이 "MirrorBit 플래시 메모리"라고 부르는 제품으로 처음 대량 생산에 들어갔다.

스판션 MirrorBit 플래시 메모리

전하 트래핑 플래시(CTF)는 2002년 AMD와 후지쓰에 의해 상용화되었다. 그 해 AMD(이후 스판션으로 분사된 부문)는 "MirrorBit"라는 새로운 플래시 메모리 기술을 발표했다. 스판션은 이 제품을 사용하여 제조 비용을 줄이고 NOR 플래시 메모리의 밀도 범위를 기존 NOR 플래시를 넘어 Intel이 제조하고 있는 다수준 셀 NOR 플래시 수준까지 끌어올릴 수 있었다.

스판션 MirrorBit 셀

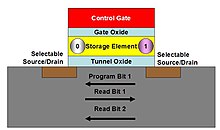

MirrorBit 셀은 전하 트래핑 층을 단순히 기존 부동 게이트의 대체품으로만 사용하는 것이 아니라, 전하 저장 질화물의 비도전성을 활용하여 동일한 메모리 셀에서 두 개의 비트를 공유할 수 있도록 한다. [그림 1]에 보이듯이 두 개의 비트는 셀의 반대쪽 끝에 위치하며, 채널을 통해 전류를 다른 방향으로 흘려보내 읽을 수 있다.

이 접근 방식을 다수준 셀 기술과 결합하여 한 셀에 4비트를 포함하는 제품도 성공적으로 제작되었다.

전하 트래핑 동작

부동 게이트 메모리 셀과 마찬가지로, 전하 트래핑 셀은 제어 게이트와 채널 사이의 가변 전하를 이용하여 트랜지스터의 문턱 전압을 변화시킨다. 이 전하를 변조하는 메커니즘은 부동 게이트와 전하 트랩 사이에 상대적으로 유사하며, 읽기 메커니즘도 매우 유사하다.

https://www.youtube.com/watch?v=5f2xOxRGKqk&pp=ygURQ2hhcmdlIHRyYXAgZmxhc2g%3D

전하 트래핑 vs. 부동 게이트 메커니즘

전하 트래핑 플래시에서 전자는 표준 플래시 메모리, EEPROM 또는 EPROM의 부동 게이트에 저장되는 것과 마찬가지로 트래핑 층에 저장된다. 핵심적인 차이점은 트래핑 층이 절연체인 반면, 부동 게이트는 도체라는 것이다.

플래시 메모리의 높은 쓰기 부하는 터널 산화물 층에 스트레스를 가해 '산화물 결함'이라고 불리는 결정 격자의 작은 교란을 일으킨다. 이러한 교란이 많이 발생하면 부동 게이트와 트랜지스터 채널 사이에 단락이 발생하여 부동 게이트가 더 이상 전하를 유지할 수 없게 된다. 이것이 플래시 메모리의 내구성 저하(플래시 메모리 항목의 '메모리 마모' 참조)의 근본 원인이다. 이러한 단락을 줄이기 위해 부동 게이트 플래시는 두꺼운 터널 산화물(~100Å)을 사용하지만, 이로 인해 Fowler-Nordheim 터널링을 사용할 때 소거 속도가 느려지고 더 높은 터널링 전압을 사용해야 하므로 다른 부분에 새로운 부담이 생긴다.

전하 트래핑 셀은 트래핑 층이 절연체이기 때문에 이러한 문제에 상대적으로 면역성이 높다. 트래핑 층과 채널 사이에 생긴 산화물 결함으로 인한 단락은 바로 접촉한 전자만 빠져나가고 나머지 전자는 그대로 남아 트랜지스터의 문턱 전압을 계속 제어할 수 있다. 단락 문제가 덜 중요하므로 터널 산화물 층을 더 얇게(50-70Å) 만들 수 있고, 이를 통해 트래핑 층과 채널의 결합도를 높여 (국부적으로 포획된 전하를 통한) 더 빠른 프로그래밍 속도와 낮은 터널링 전압으로의 소거가 가능하다. 이 낮은 터널링 전압은 터널 산화물 층에 가해지는 스트레스를 줄여 격자 교란도 줄어든다.

전하 트래핑 셀의 또 다른 중요한 장점은 얇은 트래핑 층이 인접 셀 간의 용량 결합을 줄여 성능과 스케일러빌리티를 개선할 수 있다는 것이다.

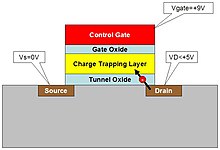

전하 트래핑 층에 전하 주입하기

전자는 채널 내 고에너지 전자(CHE) 주입 메커니즘, 즉 핫 캐리어 주입 방식을 통해 부동 게이트 NOR 플래시를 프로그래밍하는 것과 유사한 방식으로 전하 트래핑 층에 이동된다. 요약하면, 제어 게이트에는 높은 전압이 가해지고 소스와 드레인에는 중간 높은 전압이 가해지면서 소스에서 드레인으로 전류가 유도된다. 이때 드레인 근처의 고전계 영역을 통과하면서 충분한 에너지를 얻은 전자들이 채널에서 떨어져나와 전하 트래핑 층에 포획된다.

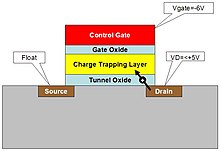

전하 트래핑 층의 전하 제거하기

전하 트래핑 플래시는 NAND 및 NOR 플래시의 소거에 사용되는 Fowler-Nordheim 터널링 방식과 달리 핫 홀 주입(핫 캐리어 주입 참조)을 통해 소거된다. 이 프로세스는 전류를 사용하는 FN 방식과 달리 전기장을 이용하여 홀을 전하 트래핑 층 쪽으로 이동시켜 전하를 제거한다.

전하 트래핑 플래시 제조

전하 트래핑 플래시는 제조 과정에서 부동 게이트 플래시와 유사하지만, 제조를 간소화하기 위한 몇 가지 예외 사항이 있다.

부동 게이트와의 소재 차이

부동 게이트 플래시와 전하 트래핑 플래시 모두 채널 바로 위에 부동 게이트 또는 전하 트래핑 층이 있고 그 위에 제어 게이트가 있는 적층 게이트 구조를 사용한다. 부동 게이트 또는 전하 트래핑 층은 채널로부터 터널 산화물 층으로, 제어 게이트로부터 게이트 산화물 층으로 절연된다. 이들 층의 소재는 저장 층을 제외하고는 모두 동일하다. 저장 층의 소재는 부동 게이트 구조에서는 도전성 폴리실리콘, 전하 트랩에서는 일반적으로 실리콘 질화물이다.

실리콘 나노크리스탈과 전하 트래핑의 관계

프리스케일 반도체는 자사의 마이크로컨트롤러(MCU) 라인에서 "박막 저장" 이라고 부르는 유사한 기술을 제조한다. 프리스케일의 접근 방식은 도전성 섬들로서의 실리콘 나노크리스탈을 절연성 실리콘 산화물 층에 사용한다.

보다 일반적인 실리콘 질화물 전하 트랩과 마찬가지로, 전자는 부동 게이트의 한쪽에서 다른쪽으로 흐르지 않기 때문에 셀의 내구성이 연장된다.

이 나노크리스탈 접근 방식은 프리스케일에 의해 대량으로 제조되고 있으며, 전반적인 전하 트래핑 저장은 ST 마이크로일렉트로닉스, 필립스, 르네사스, 삼성, 도시바, 애트멜, 스판션 등에서 개발 중이다.

부동 게이트와의 공정 차이

질화물 전하 트래핑 층이 비도전성이므로 패터닝될 필요가 없다 - 모든 전하 트랩이 이미 서로 절연되어 있다. 이를 통해 제조 과정을 간소화할 수 있다.

부동 게이트 구조는 최근 공정 세대에서 보다 정교한 게이트 유전체가 필요했고, 오늘날 일반적으로 제조가 더 복잡한 ONO(산화물-질화물-산화물) 구조를 사용하지만, 전하 트래핑 플래시에서는 필요하지 않다.

질화물 층의 장점 중 하나는 부동 게이트에 사용되는 폴리실리콘보다 고온 제조 공정에 덜 민감하다는 것이다. 이를 통해 전하 트랩 상부 층의 공정이 간소화된다.

MirrorBit 플래시 메모리

스판션의 MirrorBit 플래시와 사이펀의 NROM은 질화물의 전하 트래핑 메커니즘을 사용하여 동일한 셀에 두 개의 비트를 저장함으로써 메모리 용량을 두 배로 늘리는 플래시 메모리이다. 이는 전하 트랩 층의 양쪽에 전하를 배치하여 구현된다. 셀은 채널을 통해 순방향 및 역방향 전류를 사용하여 전하 트랩의 양쪽을 읽음으로써 읽을 수 있다.

MirrorBit 동작 – 셀에 2비트 저장하기

CHE 프로그래밍(그림 2) 동안 고에너지 전자는 채널의 바이어스된 드레인 쪽 끝에서 채널로부터 전하 트래핑 층으로 주입되지만, 부유 상태인 소스 쪽 끝에서는 그렇지 않다. 트랜지스터의 소스와 드레인을 채널의 한쪽 끝에서 다른 쪽 끝으로 전환하면, 전하를 채널의 양쪽 끝에 주입하고 저장할 수 있다.

마찬가지로, 채널의 한쪽 끝에 소거 전기장을 가하고 다른 한쪽 끝은 부유 상태로 두면(그림 3 참조) 전하 트래핑 셀의 한쪽 끝을 소거할 수 있다. Band-to-band 핫 홀 소거는 일부가 전자와 재결합하여 전하 트랩의 그 쪽 끝에서 전하를 제거하는 국소적인 홀을 발생시킨다.

셀에서 2비트 읽기

MirrorBit 읽기는 간단히 소스와 드레인 접점을 역전시켜 수행된다. 드레인 쪽에서 확장되는 접합 공핍 영역이 채널을 전하 트래핑 셀의 드레인 쪽 중첩 부분의 전하로부터 차단한다. 이로 인해 드레인 쪽 전하는 채널을 통해 흐르는 전류에 거의 영향을 미치지 않고, 오직 소스 쪽 전하만이 트랜지스터의 문턱 전압을 결정한다.

소스와 드레인을 역전시키면 반대쪽 전하가 트랜지스터의 문턱 전압을 결정한다.

이렇게 전하 트래핑 셀의 양쪽 끝에 서로 다른 두 가지 전하 수준이 있으면 전류 흐름 방향에 따라 두 가지 다른 전류가 셀을 통해 흐르게 된다.

후속 개발

https://www.youtube.com/watch?v=YtBysgPOKx4&pp=ygURQ2hhcmdlIHRyYXAgZmxhc2g%3D

전하 트래핑 NAND – 삼성전자 및 기타

2006년 삼성전자는 당시 사용되던 평면 구조와 유사한 셀 구조를 이용하여 NAND 기술의 지속적인 스케일링을 가능하게 하는 전하 트래핑 플래시 연구를 공개했다. 이 기술은 SONOS(실리콘-산화물-질화물-산화물-실리콘) 또는 MONOS(금속-ONOS) 커패시터 구조에 질화물 층의 전하 트랩에 정보를 저장하는 것에 의존한다.

삼성전자는 두 가지 셀 구조를 공개했는데, 기존 3D 캡 구조(이 문서 후반부에 자세히 설명됨)를 제조할 수 없을 것으로 믿었던 40nm 기술을 위한 TANOS(티타늄, 알루미나, 질화물, 산화물, 실리콘)와 알루미나 산화물을 공개되지 않은 높은 유전율 물질로 대체한 THNOS가 그것이다. 이 높은 유전율 물질은 알루미나 산화물 구조보다 더 긴 데이터 보존 시간을 제공할 것으로 예상되었다.

캡 구조에서 제어 게이트는 확장되어 기존 부동 게이트 셀에서 인접한 부동 게이트 사이의 장벽 역할을 한다.

그 후 5년 동안 많은 소자 설계자들이 이 캡 구조를 점점 더 작은 공정 크기로 밀어내는 방법을 찾아 이 접근법으로 30nm 노드에서 NAND를 성공적으로 생산했다.

전하 트래핑은 여전히 NAND 플래시의 미래 기술로 간주되지만, 평면 셀보다는 수직 구조에 더 고려되고 있다.

NAND가 전하 트래핑 기술이 필요한 이유

NAND 플래시는 매우 공격적으로 스케일링되어왔다(그림 4). 공정이 진화함에 따라 제어 게이트와 부동 게이트의 접면 폭은 공정 축소 제곱에 비례하여 줄어들고, 부동 게이트 간 간격은 공정 축소에 비례하여 줄어드는 반면, 부동 게이트의 두께는 그대로 유지된다(부동 게이트를 더 얇게 하면 전자 손실에 대한 내성이 줄어든다). 그 결과 인접 부동 게이트 간 결합이 제어 게이트와 부동 게이트 간 결합보다 커져 인접 비트 간 데이터 오류가 발생한다.

공정이 계속 축소되면서 이 문제는 점점 심각해지게 된다. 이러한 이유로 현대 NAND 플래시의 제어 게이트는 부동 게이트를 덮는 구조로 재구성되었다. 캡 구조에서 제어 게이트는 확장되어 기존 부동 게이트 셀에서 인접한 부동 게이트 사이의 장벽 역할을 한다(그림 5 참조). 이를 통해 부동 게이트와 제어 게이트 간 결합은 증가시키고, 인접 부동 게이트 간 결합은 감소시킬 수 있다. 단점은 제어 게이트가 채널에 결합되므로 이를 최소화하기 위한 대책이 필요하다는 것이다.

2006년에는 이 장치들이 요구하는 복잡한 3층 ONO 게이트 산화물을 생산하기 어려워 50nm 노드보다 더 작은 공정에서는 기존 부동 게이트 캡 구조를 제조할 수 없을 것으로 여겨졌다.

삼성전자는 2006년 말 2008년까지 40nm 공정 노드에서 이러한 장치를 양산할 것이라고 발표했지만, 이후 5년 동안 많은 소자 설계자들이 캡 구조를 점점 더 작은 공정 크기로 밀어내는 방법을 찾아 20nm 노드까지 이 접근법으로 NAND를 성공적으로 생산했다.

전하 트래핑 접근법은 여전히 20nm 미만 공정을 위한 NAND 플래시의 미래로 여겨지고 있으며, 평면 및 수직 3D 구조 모두에 고려되고 있다.

이 변화가 언제 일어날지

오늘날 SanDisk는 회사가 10-19nm 범위의 두 번째 노드까지 기존 NAND 구조를 계속 사용할 것으로 예상한다고 주장한다. 이는 업계가 10nm에 도달할 때까지 표준 소자 구조가 그대로 유지될 수 있음을 의미하지만, 부동 게이트를 안정적으로 생산하는 과제는 공정이 축소될수록 더 심각해진다.

반면, 반도체 기술 로드맵(ITRS)의 2010년 공정 통합, 소자 및 구조(PIDS) 표에서는 전하 트래핑이 2012년 22nm부터 채택되기 시작하여 2014년 20nm 공정에서 주류로 자리잡을 것으로 보인다.

향후 공정에는 평면 전하 트래핑 셀이 사용될 수 있다. 아직 19nm 미만 공정에 대한 제조업체의 공정은 공개되지 않았다.

수직 구조를 위한 전하 트래핑 층

수직 구조는 더 이상의 수평 스케일링이 불가능해지면 NAND 플래시의 논리적인 다음 단계로 여겨진다. 수직 특징은 옆으로 식각할 수 없기 때문에, 전하 트래핑 층은 수직 NAND 플래시 스트링을 구축하는 매우 흥미로운 방법이 된다.

도시바와 삼성전자는 수직 전하 트래핑 NAND 구조의 프로토타입을 공개했다.

도시바의 BiCS와 삼성의 3D NAND

도시바는 2007년에, 삼성은 2009년에 주어진 실리콘 면적에서 비트 수를 늘리기 위해 수평 대신 수직으로 표준 NAND 플래시 비트 스트링을 구축하는 3D V-NAND 개발을 발표했다.

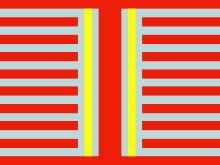

이의 단면도는 [그림 6]과 같다. 이 그림에서 빨간 부분은 도전성 폴리실리콘, 파란색은 실리콘 이산화물 절연층, 노란색은 질화물 전하 트래핑 층을 나타낸다.

수직 구조(하나만 표시)는 교대로 배열된 유전체와 전하 트래핑 층(파란색과 노란색)이 감싸고 있는 채널을 구현하는 실린더이다. 이러한 소자를 제조하기 위해 먼저 표준 CMOS 논리 소자가 포함된 실리콘 기판 위에 도전성 폴리실리콘과 실리콘 이산화물 유전체 층을 증착한다. 그 후 트렌치를 식각하고 그 벽면에 순서대로 실리콘 이산화물(파란색), 실리콘 질화물(노란색), 다시 실리콘 이산화물(파란색) 층을 증착하여 게이트 유전체, 전하 트랩, 터널 유전체를 형성한다. 마지막으로 도전성 폴리실리콘(빨간색)으로 홀을 채워 채널을 형성한다. 이 구조에서 도전성 폴리실리콘의 교대 층이 제어 게이트 역할을 한다.

이 구조는 전하 트랩 층이 각 제어 게이트 사이에 절연될 필요가 없어 수직 방향으로 식각할 필요가 없다는 점을 활용한다.

내장 메모리에서의 전하 트래핑

전하 트래핑 플래시가 다른 기술에 비해 갖는 장점 중 하나는 표준 로직 공정에 비교적 쉽게 내장될 수 있다는 것이다. 표준 로직 공정은 3개의 고전압 마스크와 3개의 핵심 CTF 마스크를 추가하여 로직 플러스 플래시 공정으로 변환할 수 있으며, 이 6개의 마스크 중 어떤 것도 임계 층(즉, 공정의 가장 최첨단 부분을 사용해야 함)이 아니다. 다른 모든 로직 공정은 직접 공유될 수 있다.

밴드갭 공학화 전하 트래핑 메모리 소자

ITRS PIDS 2013에 따르면 보존 및 소거 딜레마를 해결하기 위해서는 밴드갭 공학화된 전하 트래핑 소자가 필요한 것으로 명시되었다. 그러나 단순한 터널 산화물을 사용하는 SONOS는 NAND 응용에 적합하지 않다 - 일단 전자가 깊은 SiN 트랩 레벨에 포획되면 높은 전기장 하에서도 탈출시키기 어렵다. 소자를 빨리 소거하려면 기판의 홀을 SiN으로 주입하여 전자 전하를 중화시켜야 한다. SiO2의 홀 장벽이 높(4.1 eV)기 때문에 홀 주입 효율이 낮고 충분한 홀 전류를 얻으려면 매우 얇은 터널 산화물(2nm)을 사용해야 한다. 그러나 이런 얇은 터널 산화물은 저장 전자에 의해 생성된 약한 내부 전기장으로 인해 기판에서의 직접 홀 터널링을 막을 수 없어 데이터 보존 성능이 나쁘다(직접 터널링 속도는 장벽 두께의 강한 함수이지만 전기장에는 약하게 의존함).

SONOS의 여러 변형이 제안되었다. 터널 유전체 공학 개념을 사용하여 터널 장벽 특성을 수정해 "가변 두께" 터널 유전체를 만들었다. 예를 들어 단일 산화물을 대신해 3층의 초박막(1-2nm) ONO층을 도입했다(BE-SONOS). 높은 전기장 하에서 상위 두 층의 산화물과 질화물은 Si 가전자대 위에 배치되어 기판의 홀이 아래 얇은 산화물을 쉽게 통과해 위의 두꺼운 SiN 트래핑 층으로 주입된다. 데이터 저장 모드에서는 약한 전기장이 3층을 상쇄하지 않아 SiN의 전자와 기판의 홀이 3층 전체 두께에 의해 차단된다. 이후 BE-SONOS에 고-k(Al2O3) 및 금속 게이트를 추가하여 소거 성능을 향상시킨 BE-MANOS가 등장했다. SiN과 고-k Al2O3 사이에 완충 산화물을 추가해 보존 성능을 개선했다. 현재 양산 3D NAND는 각 업체별로 세부 레시피를 조정한 BE-MANOS와 유사한 구조를 채택하고 있다. 터널 장벽을 위한 밴드갭 공학화 개념은 전하 트래핑 소자에 필수적인 것으로 인정되고 있다.

전하 트래핑 NAND가 GCR 및 FG 간섭 문제를 해결하여 20nm 미만으로의 축소를 약속하지만, 워드라인 절연파괴 및 전자 수 부족과 같은 근본적인 한계를 해결하지는 못한다. 따라서 로드맵 추세상 평면 FG와 3D NAND 사이의 전환 역할을 한다. 전하 트래핑 소자를 3D NAND 구축에 사용하면 더 큰 소자 크기로 인해 전자 수와 워드라인 절연파괴 문제가 자연스럽게 해결된다.

https://www.youtube.com/watch?v=GwWHA11R7yk&pp=ygURQ2hhcmdlIHRyYXAgZmxhc2g%3D

'반도체 > 전공정' 카테고리의 다른 글

| [📚세미피디아] High NA EUV란? (0) | 2024.04.18 |

|---|---|

| [📚세미피디아] Reactive-ion etching, Deep reactive-ion etching이란? (0) | 2024.04.16 |

| [📚세미피디아] Threshold voltage란? (0) | 2024.04.13 |

| [📚세미피디아] EUV란? (Extreme ultraviolet lithography) (0) | 2024.04.11 |

| [📚세미피디아] 광학 근접 보정(Optical Proximity Correction, OPC)이란? (0) | 2024.04.10 |